# Single-Wire-Transceiver

# Preliminary Data Sheet

#### 1 Overview

#### 1.1 Features

- Single-wire transceiver, suitable for LIN protocol

- Compatible to LIN specification

- Compatible to ISO 9141 functions

- Transmission rate up to 20 kBaud

- Very low current consumption in stand-by mode

- Short circuit proof to ground and battery

- Overtemperature protection

| Туре       | Ordering Code | Package   |

|------------|---------------|-----------|

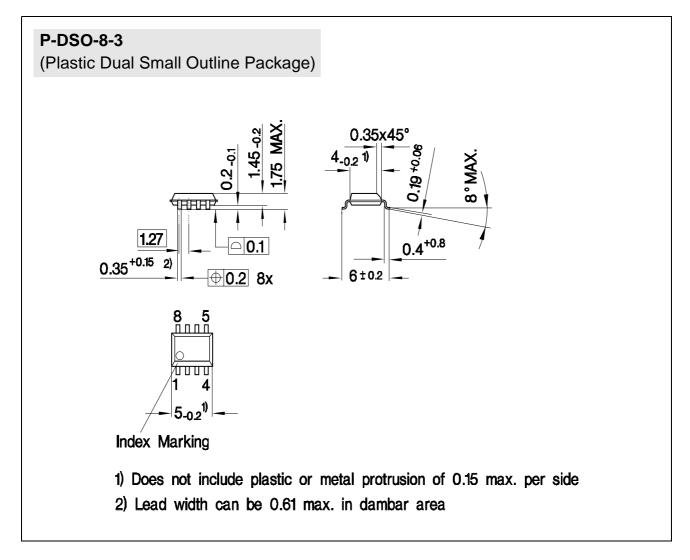

| TLE 6258 G | Q67006-A9469  | P-DSO-8-3 |

#### Description

The single-wire transceiver TLE 6258 is a monolithic integrated circuit in a P-DSO-8-3 package. It works as an interface between the protocol controller and the physical bus. The TLE 6258 is especially suitable to drive the bus line in LIN systems in automotive and industrial applications. Further it can be used in standard ISO9141 systems.

In order to reduce the current consumption the TLE 6258 offers a stand-by mode. A wake-up caused by a message on the bus sets the RxD output low until the device is switched to normal operation mode.

The IC is based on the Siemens Power Technology SPT<sup>®</sup> which allows bipolar and CMOS control circuitry in accordance with DMOS power devices existing on the same monolithic circuit.

The TLE 6258 is designed to withstand the severe conditions of automotive applications.

TLE 6258

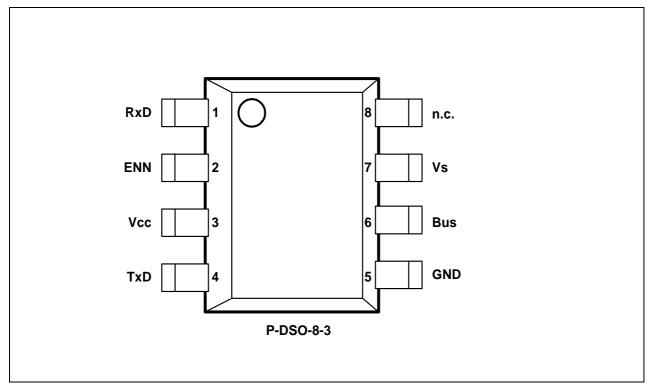

## **1.2 Pin Configuration** (top view)

## Figure 1: Pinout

# 1.3 Pin Definitions and Functions

| Pin No. | Symbol          | Function                                                                                                 |

|---------|-----------------|----------------------------------------------------------------------------------------------------------|

| 1       | RxD             | Receive data output; integrated pull up, LOW in dominant state,                                          |

| 2       | ENN             | <b>Enable not input;</b> integrated 30 k $\Omega$ pull up, transceiver in normal operation mode when LOW |

| 3       | V <sub>CC</sub> | 5V supply input;                                                                                         |

| 4       | TxD             | Transmit data input; integrated pull up, LOW in dominant state                                           |

| 5       | GND             | Ground;                                                                                                  |

| 6       | Bus             | <b>Bus output/input;</b> internal 30 k $\Omega$ pull up, LOW in dominant state                           |

| 7       | Vs              | Battery supply input;                                                                                    |

| 8       | n.c.            | not connected                                                                                            |

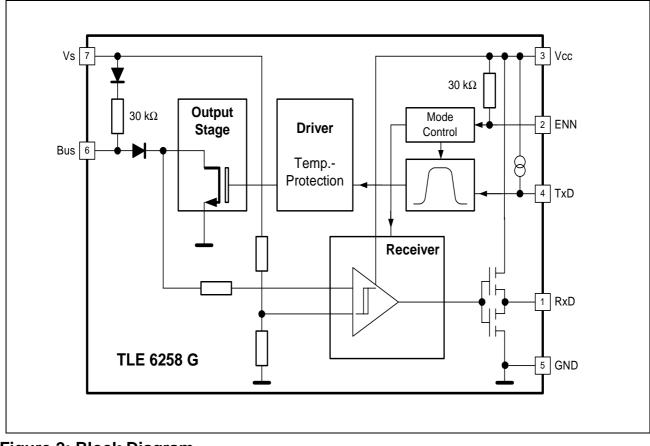

## 1.4 Functional Block Diagram

Figure 2: Block Diagram

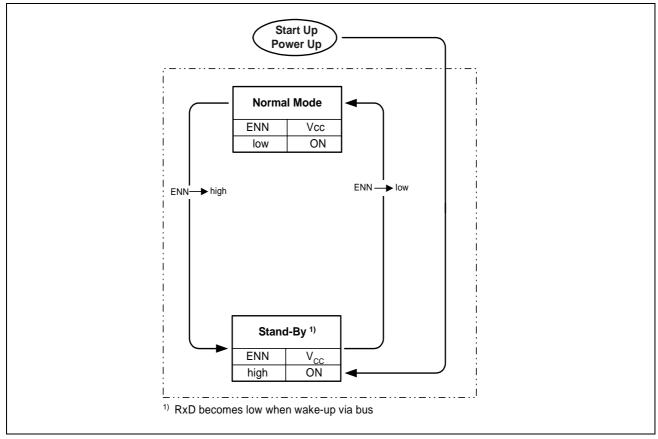

#### 1.5 Application Information

Figure 3: State Diagram

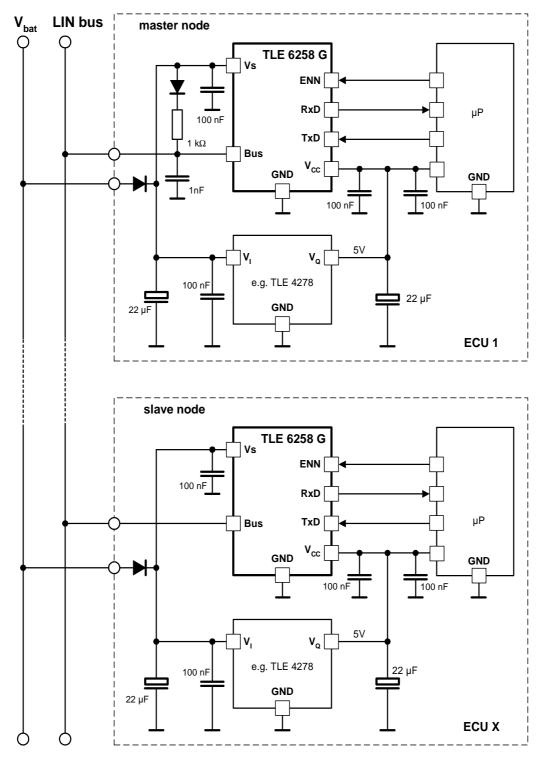

For fail safe reasons the TLE6258 has already a pull up resistor of  $30k\Omega$  implemented. To achieve the required timings for the dominant to recessive transition of the bus signal an additional external termination resistor of  $1k\Omega$  is required. It is recommended to place this resistor in the master node. To avoid reverse currents from the bus line into the battery supply line in case of an unpowered node, it is recommended to place a diode in series to the external pull up. For small systems (low bus capacitance) the EMC performance of the system is supported by an additional capacitor of at least 1nF in the master node (see figure 6, application circuit).

In order to reduce the current consumption the TLE 6258 offers a stand-by mode. This mode is selected by switching the Enable Not (ENN) input high (see figure 3, state diagram). In the stand-by mode a wake-up caused by a message on the bus is indicated by setting the RxD output low. When entering the normal mode this wake-up flag is reset and the RxD output is released to transmit the bus data.

#### 2 Electrical Characteristics

#### 2.1 Absolute Maximum Ratings

| Parameter | Symbol | Limit Values |      | Unit | Remarks |

|-----------|--------|--------------|------|------|---------|

|           |        | min.         | max. |      |         |

#### Voltages

| Supply voltage                             | V <sub>cc</sub> | -0.3 | 6                        | V  |                                               |

|--------------------------------------------|-----------------|------|--------------------------|----|-----------------------------------------------|

| Battery supply voltage                     | Vs              | -0.3 | 40                       | V  |                                               |

| Bus input voltage                          | $V_{ m bus}$    | -20  | 32                       | V  |                                               |

| Bus input voltage                          | $V_{ m bus}$    | -20  | 40                       | V  | t < 1 s                                       |

| Logic voltages at<br>EN, TxD, RxD          | V               | -0.3 | V <sub>cc</sub><br>+ 0.3 | V  | 0 V < V <sub>CC</sub> < 5.5 V                 |

| Electrostatic discharge voltage at Vs, Bus | $V_{\rm ESD}$   | -4   | 4                        | kV | human body model<br>(100 pF via 1.5 kΩ)       |

| Electrostatic discharge voltage            | $V_{ESD}$       | -2   | 2                        | kV | human body model (100 pF via 1.5 k $\Omega$ ) |

| Temperatures                               |                 |      |                          |    |                                               |

| Junction temperature                       | Tj              | -40  | 150                      | °C | -                                             |

|                                            |                 | •    |                          |    |                                               |

Note: Maximum ratings are absolute ratings; exceeding any one of these values may cause irreversible damage to the integrated circuit.

# 2.2 Operating Range

| Parameter              | Symbol          | nbol Limit Values |      | Unit | Remarks |  |

|------------------------|-----------------|-------------------|------|------|---------|--|

|                        |                 | min.              | max. |      |         |  |

| Supply voltage         | V <sub>CC</sub> | 4.5               | 5.5  | V    |         |  |

| Battery Supply Voltage | Vs              | 6                 | 20   | V    |         |  |

| Junction temperature   | Tj              | - 40              | 150  | °C   | -       |  |

# Thermal Shutdown (junction temperature)

| Thermal shutdown temp. | $T_{\rm jSD}$ | 150 | 170 | 190 | °C |

|------------------------|---------------|-----|-----|-----|----|

| Thermal shutdown hyst. | $\Delta T$    | _   | 10  | _   | К  |

#### **Thermal Resistances**

| Junction ambient | $R_{ m thj-a}$ | _ | 185 | K/W | - |

|------------------|----------------|---|-----|-----|---|

|------------------|----------------|---|-----|-----|---|

#### 2.3 Electrical Characteristics

$4.5 \text{ V} < V_{CC} < 5.5 \text{ V}; 6.0 \text{ V} < V_{S} < 20 \text{ V}; R_{L} = 1 \text{ k}\Omega; V_{ENN} < V_{ENN,ON}; -40 \text{ °C} < T_{j} < 125 \text{ °C}; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.}$

| Parameter | Symbol | Limit Values |      |      | Unit | Remark |

|-----------|--------|--------------|------|------|------|--------|

|           |        | min.         | typ. | max. |      |        |

#### **Current Consumption**

| Current consumption | I <sub>CC</sub>   | 0.5 | 1.5 | mA | recessive state;<br>V <sub>TxD</sub> = V <sub>CC</sub> |

|---------------------|-------------------|-----|-----|----|--------------------------------------------------------|

| Current consumption | I <sub>S</sub>    | 0.5 | 1.0 | mA | recessive state;<br>V <sub>TxD</sub> = V <sub>CC</sub> |

| Current consumption | I <sub>CC</sub>   | 0.7 | 2.0 | mA | dominant state;<br>V <sub>TxD</sub> = 0 V              |

| Current consumption | Is                | 0.7 | 1.5 | mA | dominant state;<br>V <sub>TxD</sub> = 0 V              |

| Current consumption | I <sub>CC</sub>   | 20  | 30  | μA | stand-by mode;<br><i>T</i> <sub>j</sub> = 25 °C        |

| Current consumption | I <sub>S</sub>    | 20  | 30  | μA | stand-by mode;<br><i>T</i> <sub>j</sub> = 25 °C        |

| Current consumption | I <sub>CC</sub>   | 20  | 40  | μA | stand-by mode                                          |

| Current consumption | Is                | 20  | 40  | μA | stand-by mode                                          |

| Current consumption | I <sub>SCC0</sub> | 16  | 30  | μA | stand-by mode, $V_{CC} = 0 V, V_S = 13.5 V$            |

#### **Receiver Output R×D**

| HIGH level output current | I <sub>RD,H</sub> |     | -0.7 | -0.4 | mA | $V_{\rm RD}$ = 0.8 x V <sub>CC</sub> ,         |

|---------------------------|-------------------|-----|------|------|----|------------------------------------------------|

| LOW level output current  | I <sub>RD,L</sub> | 0.4 | 0.7  |      | mA | $V_{\text{RD}} = 0.2 \text{ x V}_{\text{CC}},$ |

#### **Bus receiver**

| Receiver threshold voltage, recessive to dominant edge | V <sub>bus,rd</sub>  | 0.44<br>x V <sub>S</sub> | 0.48<br>x V <sub>S</sub> |                          | V  | -8 V < V <sub>bus</sub> < V <sub>bus,dom</sub>                        |

|--------------------------------------------------------|----------------------|--------------------------|--------------------------|--------------------------|----|-----------------------------------------------------------------------|

| Receiver threshold voltage, dominant to recessive edge | V <sub>bus,dr</sub>  |                          | 0.52<br>x V <sub>S</sub> | 0.56<br>x V <sub>S</sub> | V  | $V_{\rm bus,rec} < V_{\rm bus} < 20$ V                                |

| Receiver hysteresis                                    | V <sub>bus,hys</sub> | 0.02<br>x V <sub>S</sub> | 0.04<br>x V <sub>S</sub> | 0.06<br>x V <sub>S</sub> | mV | V <sub>bus,hys</sub> =<br>V <sub>bus,rec</sub> - V <sub>bus,dom</sub> |

| wake-up threshold voltage                              | V <sub>wake</sub>    | 0.40x<br>V <sub>S</sub>  | 0.55x<br>V <sub>S</sub>  | 0.65x<br>V <sub>S</sub>  | V  |                                                                       |

## 2.3 Electrical Characteristics (cont'd)

$4.5 \text{ V} < V_{CC} < 5.5 \text{ V}; 6.0 \text{ V} < V_{S} < 20 \text{ V}; R_{L} = 1 \text{ k}\Omega; V_{ENN} < V_{ENN,ON}; -40 \text{ °C} < T_{j} < 125 \text{ °C}; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.}$

| Parameter | Symbol | Limit Values |      |      | Unit | Remark |

|-----------|--------|--------------|------|------|------|--------|

|           |        | min.         | typ. | max. |      |        |

#### Transmission Input T×D

| HIGH level input voltage threshold | V <sub>TD,H</sub> |                          | 2.8  | 0.7 x<br>V <sub>CC</sub> | V  | recessive state            |

|------------------------------------|-------------------|--------------------------|------|--------------------------|----|----------------------------|

| TxD input hysteresis               | $V_{TD,hys}$      | 300                      | 600  |                          | mV |                            |

| LOW level input voltage threshold  | V <sub>TD,L</sub> | 0.3 x<br>V <sub>CC</sub> | 2.2  |                          | V  | dominant state             |

| TxD pull up current                | $I_{\rm TD}$      | -150                     | -110 | -80                      | μA | V <sub>TxD</sub> < 0.3 Vcc |

#### **Bus transmitter**

| Bus recessive output voltage | $V_{\rm bus,rec}$      | 0.9 x          |      | VS  | V  | $V_{TxD} = V_{CC}$                                                                                         |

|------------------------------|------------------------|----------------|------|-----|----|------------------------------------------------------------------------------------------------------------|

| Bus dominant output voltage  | $V_{\sf bus, \sf dom}$ | V <sub>S</sub> |      | 1.5 | V  | $V_{TxD} = 0 V;$                                                                                           |

| Bus short circuit current    | I <sub>bus,sc</sub>    | 40             | 85   | 125 | mA | $V_{\text{bus,short}} = 13.5 \text{ V}$                                                                    |

| Leakage current              | I <sub>bus,lk</sub>    | -350           | -260 |     | μA | $V_{\rm CC} = 0 \text{ V}, V_{\rm S} = 0 \text{ V}, V_{\rm bus} = -8 \text{ V}, T_{\rm j} < 85 \text{ °C}$ |

|                              |                        |                | 5    | 20  | μA | $V_{\rm CC} = 0 \text{ V}, V_{\rm S} = 0 \text{ V}, V_{\rm bus} = 20 \text{ V}, T_{\rm j} < 85 \text{ °C}$ |

| Bus pull up resistance       | R <sub>bus</sub>       | 20             | 30   | 47  | kΩ |                                                                                                            |

#### Enable not input (pin ENN)

| HIGH level input voltage threshold | $V_{ENN,off}$    |                          | 2.8 | 0.7 x<br>V <sub>CC</sub> | V  | low power mode           |

|------------------------------------|------------------|--------------------------|-----|--------------------------|----|--------------------------|

| LOW level input voltage threshold  | $V_{ENN,on}$     | 0.3 x<br>V <sub>CC</sub> | 2.2 |                          | V  | normal operation<br>mode |

| ENN input hysteresis               | $V_{ENN,hys}$    | 300                      | 600 |                          | mV |                          |

| ENN pull up resistance             | R <sub>ENN</sub> | 15                       | 30  | 60                       | kΩ |                          |

#### **2.3 Electrical Characteristics** (cont'd)

4.5 V <  $V_{CC}$  < 5.5 V; 6.0 V <  $V_S$  < 20 V;  $R_L$  = 1 k $\Omega$ ;  $V_{ENN}$  <  $V_{ENN,ON}$ ; -40 °C <  $T_j$  < 125 °C; all voltages with respect to ground; positive current flowing into pin; unless otherwise specified.

| Parameter | Symbol | Limit Values |      |      | Unit | Remark |

|-----------|--------|--------------|------|------|------|--------|

|           |        | min.         | typ. | max. |      |        |

#### **Dynamic Transceiver Characteristics**

| falling edge slew rate                                          | S <sub>bus(L)</sub>  | -3 | -2.0 | -1  | V/µs | $\begin{array}{l} 80\% > V_{bus} > 20\% \\ C_{bus} = 3.3 \ nF; \\ \mathcal{T}_{ambient} < 85 \ ^{\circ}\text{C} \\ V_{CC} = 5 \ V; \ V_{S} = 13.5 \ V \end{array}$ |

|-----------------------------------------------------------------|----------------------|----|------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rising edge slew rate                                           | S <sub>bus(H)</sub>  | 1  | 1.5  | 3   | V/µs | $\begin{array}{l} 20\% < V_{bus} < 80\% \\ C_{bus} = 3.3 \ \mathrm{nF}; \\ V_{CC} = 5 \ \mathrm{V}; \ \mathrm{V}_{\mathrm{S}} = 13.5 \ \mathrm{V} \end{array}$     |

| Propagation delay<br>TxD-to-RxD LOW (recessive<br>to dominant)  | t <sub>d(L),TR</sub> | 2  | 4    | 6   | μs   | $C_{\text{bus}} = 3.3\text{nF};$<br>$V_{\text{CC}} = 5\text{V}; V_{\text{S}} = 13.5\text{V}$<br>$C_{\text{RxD}} = 20 \text{ pF}$                                   |

| Propagation delay<br>TxD-to-RxD HIGH (dominant<br>to recessive) | t <sub>d(H),TR</sub> | 2  | 4    | 6   | μs   | $C_{bus} = 3.3 \text{ nF};$<br>V <sub>CC</sub> = 5 V; V <sub>S</sub> = 13.5V<br>$C_{RxD} = 20 \text{ nF}$                                                          |

| Propagation delay<br>TxD LOW to bus                             | t <sub>d(L),T</sub>  |    | 1    | 4   | μs   | V <sub>CC</sub> = 5 V                                                                                                                                              |

| Propagation delay<br>TxD HIGH to bus                            | t <sub>d(H),T</sub>  |    | 1    | 4   | μs   | V <sub>CC</sub> = 5 V                                                                                                                                              |

| Propagation delay bus dominant to RxD LOW                       | t <sub>d(L),R</sub>  |    | 0.5  | 2.0 | μs   | $V_{CC} = 5V;$<br>$C_{RxD} = 20pF$                                                                                                                                 |

| Propagation delay<br>bus recessive to RxD HIGH                  | t <sub>d(H),R</sub>  |    | 0.5  | 2.0 | μs   | $V_{CC} = 5 V;$<br>$C_{RxD} = 20 \text{ pF}$                                                                                                                       |

| Receiver delay symmetry                                         | t <sub>sym,R</sub>   | -2 |      | 2   | μs   | $t_{\text{sym},\text{R}} = t_{d(L),\text{R}} - t_{d(H),\text{R}}$                                                                                                  |

| Transmitter delay symmetry                                      | t <sub>sym,T</sub>   | -2 |      | 2   | μs   | $t_{\text{sym},\text{T}} = t_{d(L),\text{T}} - t_{d(H),\text{T}}$                                                                                                  |

| Wake-up delay time                                              | t <sub>wake</sub>    | 30 | 70   | 150 | μs   |                                                                                                                                                                    |

## 3 Diagrams

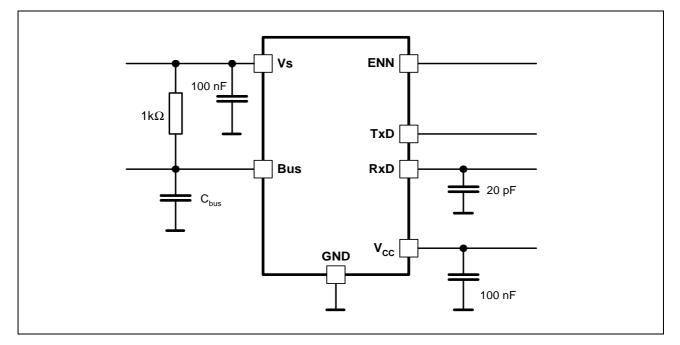

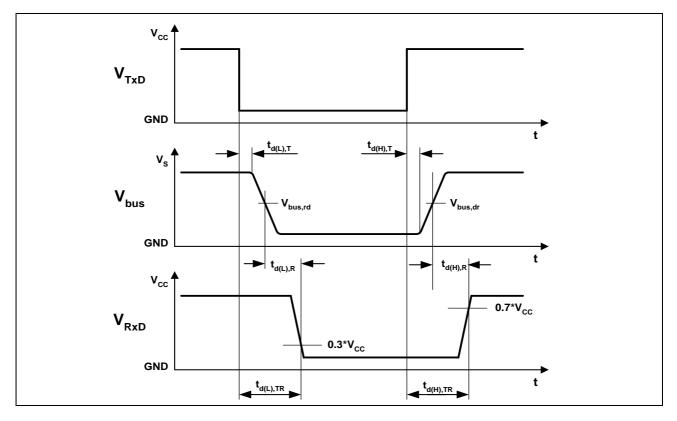

#### Figure 4: Test circuits

Figure 5: Timing diagrams for dynamic characteristics

# 4 Application

**Figure 6: Application Circuit**

#### 5 Package Outlines

#### Sorts of Packing

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device

Dimensions in mm

Edition 1999-10-12

Published by Infineon Technologies AG St.-Martin-Strasse 53 D-81541 München

<sup>©</sup> Infineon Technologies AG1999 All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.